Tang Primer 25K FPGA 开发踩坑指南

本文记录了在使用 Tang Primer 25K (GW5A-LV25MG121NC1/I0) 开发 SWD 调试器时遇到的问题及解决方案。

开发环境

- 开发板: Tang Primer 25K + Dock 扩展板

- 芯片: GW5A-LV25MG121NC1/I0 (GW5A-25B)

- IDE: Gowin FPGA Designer

- 时钟: 50MHz 晶振 (E2 引脚)

坑1: E2 时钟引脚报错 (PR2017)

错误现象

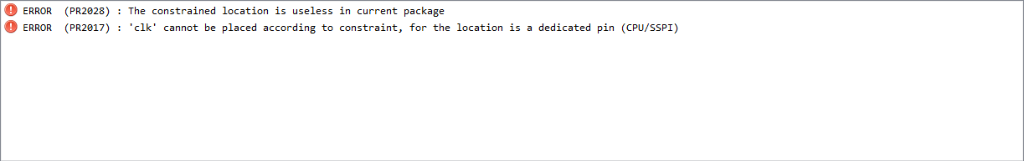

Place & Route 阶段报错:

ERROR (PR2028): The constrained location is useless in current package

ERROR (PR2017): 'clk' cannot be placed according to constraint, for the location is a dedicated pin (CPU/SSPI)

问题原因

E2 引脚在 GW5A-25B 芯片上是双用途引脚 (Dual-Purpose Pin),默认被分配给 CPU/SSPI 配置功能,不能直接用作普通 GPIO 或时钟输入。

解决方案

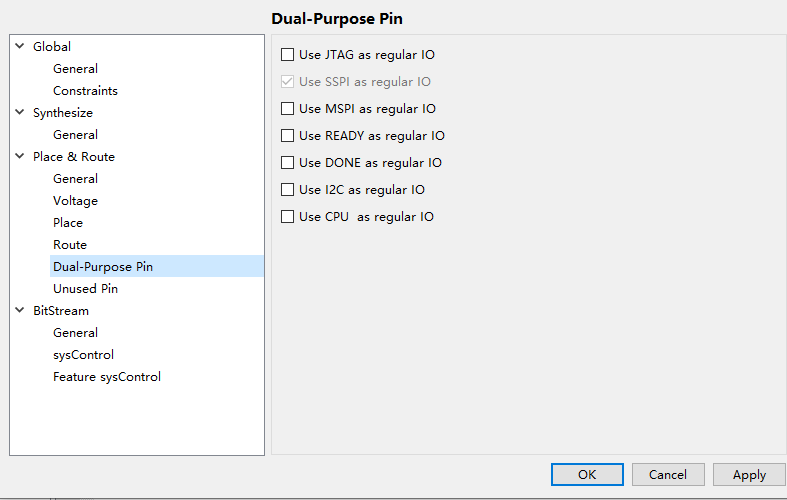

在 Gowin IDE 中修改项目配置,将双用途引脚释放为普通 IO:

- 菜单 Project → Configuration

- 左侧选择 Place & Route → Dual-Purpose Pin

- 同时勾选以下两个选项:

- ✅ Use SSPI as regular IO

- ✅ Use CPU as regular IO

- 点击 OK 保存

⚠️ 注意: 仅勾选 SSPI 选项是不够的,必须同时勾选 CPU 选项,因为 E2 引脚同时绑定了这两个功能。

本文是原创文章,采用 CC BY-NC-ND 4.0 协议,完整转载请注明来自 asher

评论

匿名评论

隐私政策

你无需删除空行,直接评论以获取最佳展示效果